实验任务:

将数据(data_in),存入ddr,然后读出,验证输入输出数据是否相等。

前言

接上一篇(3)MIG的使用教程

MIG配置如下:

- 系统时钟sys_clk = 200Mhz

- 系统复位sys_rst 低有效

- 模式:4:1

- 位宽:

注:由于选择的DDR3的突然长度为8,所以mig的数据位宽=16*8=128bit,对应到代码即app_wdf_data[127:0] , app_rd_data[127:0]。

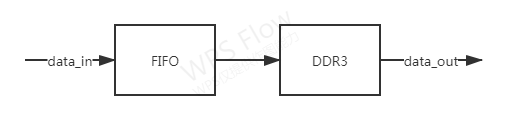

系统方案

2.1方案设计

实验任务:

将数据(data_in),存入ddr,然后读出,验证输入输出数据是否相等。

实验目的:

初步掌握DDR读写设计。

为什么要先过FIFO再写入DDR?

因为DDR接口对用户而言并不是一直有效,只有等DDR“有效”时(app_rdy = 1 && app_wdf_rdy = 1),才能进行写入。

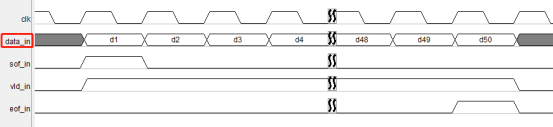

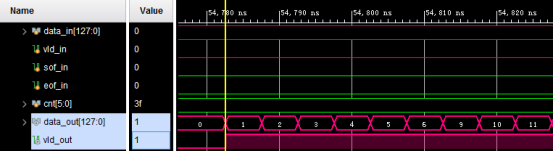

2.1.1输入接口时序图

输入数据为1-50共50个数据,以vld_in信号表征输入数据有效。

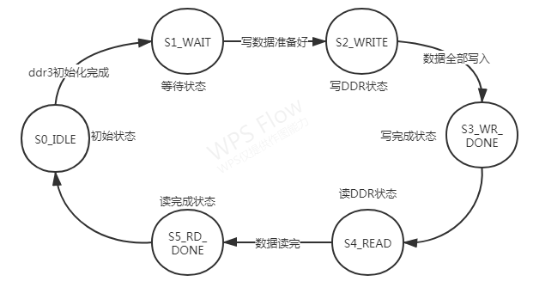

2.2状态机设计

2.2.1独热码

//代码块

2.2.2状态机流程图

2.2.3三段式状态机

//代码块

代码很简单,此处不再嗦。

2.3app接口设计

//daimakuai

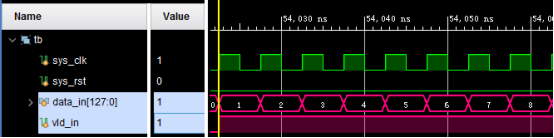

仿真结果

因为DDR仿真,需要用到ddr3_model,单开一篇来讲解。

这里只看仿真结果。

输入数据: 1-50;

输出数据: 1-50;

DDR读写测试成功!