@

目录

ARMV8系统级编程模型主要包括异常级别、运行状态、安全状态、同步异常、异步异常、DEBUG等。本文主要对系统级编程模型做一个概要介绍。

1. 典型的Exception Level使用模型

| 异常级别 | 运行的软件 |

|---|---|

| EL0 | Secure or Non-secure application |

| EL1 | Secure or Non-secure OS |

| EL2 | Hypervisor (可以理解为上面跑多个虚拟OS) |

| EL3 | Secure Monitor(ARM Trusted Firmware) |

2.异常相关术语

| 术语 | 说明 |

|---|---|

| Taking an exception | PE第一次回应一个异常,此时PE state称为taken from, 之后PE状态为taken to |

| Returning from exception | 当异常返回指令被提交运行,PE state就是return from exception |

| 异常级别 | 不同异常级别优先级不同,如EL3的异常高于EL1的异常 |

| 精准异常(precise exception) | 找到某条指令,这条指令前的所有指令都执行完毕,这条指令之后的所有指令都未执行(执行的需要回退),这样PE状态就被记录下载,异常处理完成后就可以恢复。除了SError irq 之外,其它的都是精准异常 |

| 同步异常(synchronous exception ) | (1)异常的产生是和cpu core执行的指令或者试图执行相关 (2)硬件提供给handler的返回地址就是产生异常的那一条指令所在的地址 (3)synchronous exception又可以细分成两个类别: a) 一种我们称之为synchronous abort,例如未定义的指令、data abort、prefetch instruction abort、SP未对齐异常,debug exception等等; b) 另一种是正常指令执行造成的,包括SVC/HVC/SMC指令,这些指令的使命就是产生异常。 |

| 异步异常(asynchronousexception ) | asynchronous exception基本上可以类似大家平常说的中断,它是毫无预警的,丝毫不考虑cpu core感受的外部事件(需要注意的是:外部并不是表示外设,这里的外部是针对cpu core而言,有些中断是来自SOC的其他HW block,例如GIC,这时候,对于processor或者cpu(指soc)而言,这些事件是内部的),这些事件打断了cpu core对当前软件的执行,因此称之interrupt。interrupt或者说asynchronous exception有下面的特点: (1)异常和CPU执行的指令无关。 (2)返回地址是硬件保存下来并提供给handler,以便进行异常返回现场的处理。这个返回地址并非产生异常时的指令。 根据这个定义IRQ、FIQ和SError interrupt属于asynchronous exception。 |

| SError interrupt | SError interrupt是发生了external abort导致的异步异常(或称中断)。 external abort来自memory system, 是访问外部memory system产生的异常(当然不是所有的来自memory system的abort都是external abort,例如来自MMU的abort就不是external abort,这里的external是针对processor而非cpu core而言,因此MMU实际上是internal的)。external abort发生在processor通过bus访问memory的时候(可能是直接对某个地址的读或者写,也可能是取指令导致的memory access),processor在bus上发起一次transaction,在这个过程中发生了abort,abort来自processor之外的memory block、device block或者interconnection block,用来告知processor,搞不定了,你自己看着办吧。external abort可以被实现成synchronous exception(precise exception),也可以实现成asynchronous exception(imprecise exception)。如果external abort是asynchronous的,那么它可以通过SError interrupt来通知cpu core |

3. Execution State

3.1 两种Execution State

ARMv8 提供AArch32 state和 AArch64 state 两种Execution State,下表是两种Execution State对比:

| Execution State | 说明 |

|---|---|

| AArch32 | 提供13个32bit通用寄存器R0-R12,一个32bit PC指针 (R15)、堆栈指针SP (R13)、链接寄存器LR (R14) |

| 提供一个32bit异常链接寄存器ELR, 用于Hyp mode下的异常返回 | |

| 提供32个64bit SIMD向量和标量floating-point支持 | |

| 提供两个指令集A32(32bit)、T32(16/32bit) | |

| 兼容ARMv7的异常模型 | |

| 协处理器只支持CP10\CP11\CP14\CP15 | |

| AArch64 | 提供31个64bit通用寄存器X0-X30(W0-W30),其中X30是程序链接寄存器LR |

| 提供一个64bit PC指针、堆栈指针SPx 、异常链接寄存器ELRx | |

| 提供32个128bit SIMD向量和标量floating-point支持 | |

| 定义ARMv8异常等级ELx(x<4),x越大等级越高,权限越大) | |

| 定义一组PE state寄存器PSTATE(NZCV/DAIF/CurrentEL/SPSel等),用于保存PE当前的状态信息 | |

| 没有协处理器概念 |

3.2 决定Execution State的寄存器

| 寄存器及bit位 | 说明 |

|---|---|

| SPSR_EL1.M[4], Saved Program Status Register (EL1) | 决定EL0的执行状态: (1) 0b1 :AArch32 execution state (2) 其它 :AArch64 execution state |

| HCR_EL2.RW, bit [31], Hypervisor Configuration Register | 决定EL1的执行状态: (1) 0b0 :较低的级别都是AArch32 (2) 0b1 :EL1的执行状态为AArch64。 在EL0上执行时,EL0的执行状态由PSTATE.nRW的当前值确定。 |

| SCR_EL3.RW, bit [10], Secure Configuration Register | 决定EL2或EL1的执行状态: (1) 0b0 :较低的级别都是AArch32 (2) 0b1 :下一层较低的异常级别是AArch64 |

| SPSR_EL3.M[4], Saved Program Status Register (EL3) | 决定EL3的执行状态: (1) 0b1 :AArch32 (2) 0b0 :AArch64 |

AArch32和AArch64之间的执行状态切换只能通过发生异常或者系统Reset来实现。

4. Secure state

| Secure state | 说明 |

|---|---|

| Non-secure | EL0/EL1/EL2, 只能访问Non-secure 物理地址空间 |

| Secure | EL0/EL1/EL3, 可以访问Non-secure 物理地址空间 & Secure 物理地址空间,可起到物理屏障安全隔离作用 |

4.1 EL3对secure state的影响

| EL3是否实现 | 说明 |

|---|---|

| 实现EL3 | (1) EL3只有secure state; (2) Non Secure state到secure state只能发生在EL3接收到异常; (3) secure state到non secure state只能发生在异常从EL3返回; (4) 如果 FEAT_SEL2未实现,EL2只有non secure state. (5) 如果 FEAT_SEL2实现,EL2可以存在 secure state,并通过SCR_EL3.EEL2 比特位置 1来使能 |

| 未实现EL3 | (1) 如果没有实现EL2,则secure state由SOC厂商决定; 2) 如果实现EL2且未实现 FEAT_SEL2, 则只有non secure state |

4.2 EL3使用AArch64 or AArch32的影响

| EL3是否实现 | 说明 |

|---|---|

| Common | (1) User mode(AArch32才有) 只执行在Non- Secure EL0 or Secure EL0; (2) EL2只有Non-secure state( FEAT_SEL2未实现时); (3) EL0 既有Non-secure state 也有Secure state |

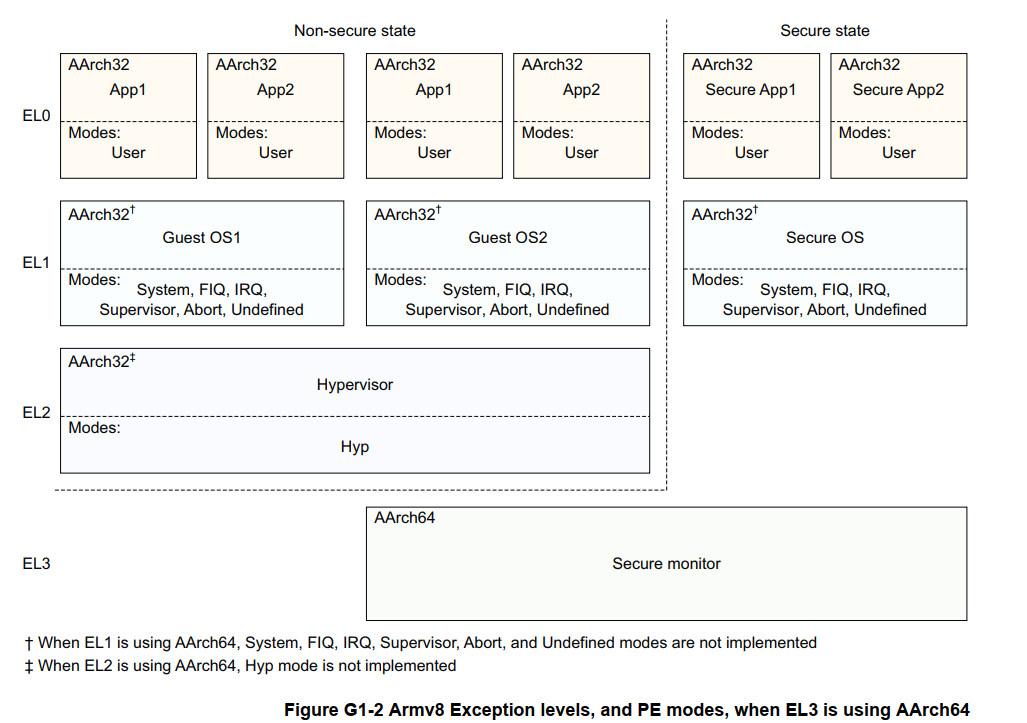

| EL3处于AArch64执行状态 | (1) 若EL1使用AArch32,那么Non-Secure {SYS/FIQ/IRQ/SVC/ABORT/UND} 模式执行在Non-secure EL1,Secure {SYS/FIQ/IRQ/SVC/ABORT/UND}模式执行在Secure EL1; (2) 若 SCR_EL3.NS = = 0,则切换到Secure EL0/EL1状态,否则切换到Non-secure EL0/EL1状态; 当SCR_EL3.{EEL2, NS} =={1,0},那么EL2也处于Secure状态 (3) Secure state 通常只有Secure EL0/EL1/EL3,但是在实现FEAT_SEL2的前提下EL2也可以处于Secure; (4) SCR.NS决定的是low level EL的secure/non-secure状态,不是决定当前的; |

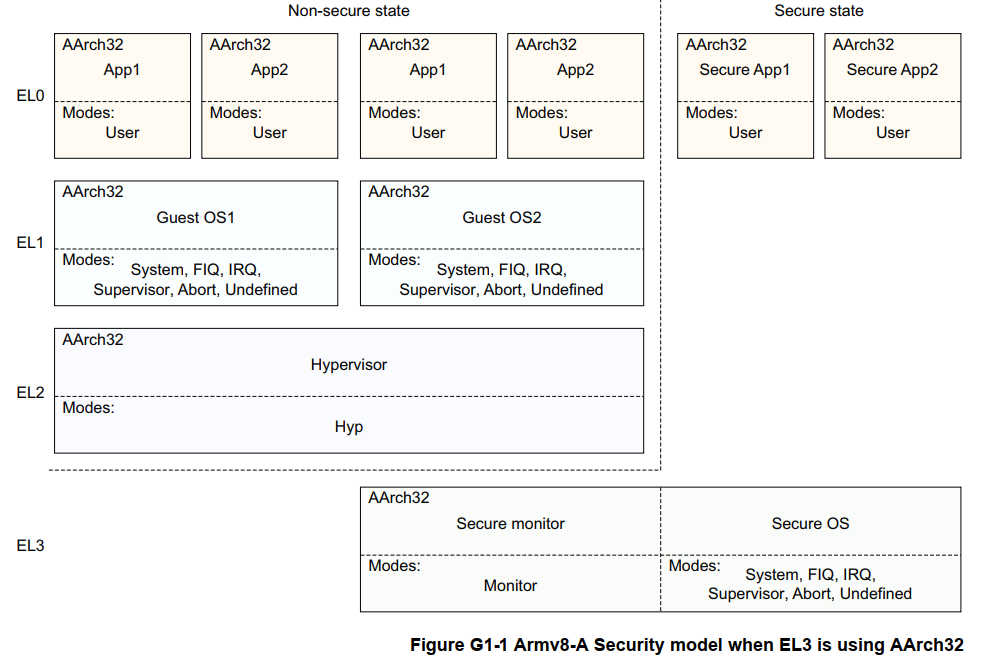

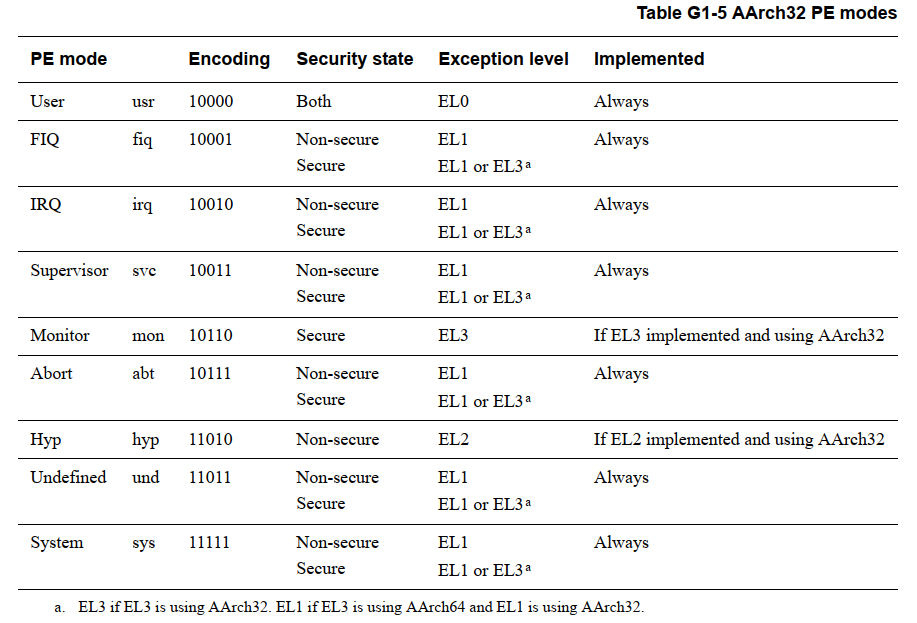

| EL3处于AArch32执行状态 | (1) 若EL1使用AArch32,那么Non- Secure {SYS/FIQ/IRQ/SVC/ABORT/UND} 模式执行在Non-secure EL1,Secure {SYS/FIQ/IRQ/SVC/ABORT/UND}模式执行在EL3; (2) Secure state只有Secure EL0/EL3,没有Secure EL1 ; (3) SCR_EL3.NS决定的是low level EL的secure/non-secure状态,不是决定当前的; |

5. execution state与secure state组合

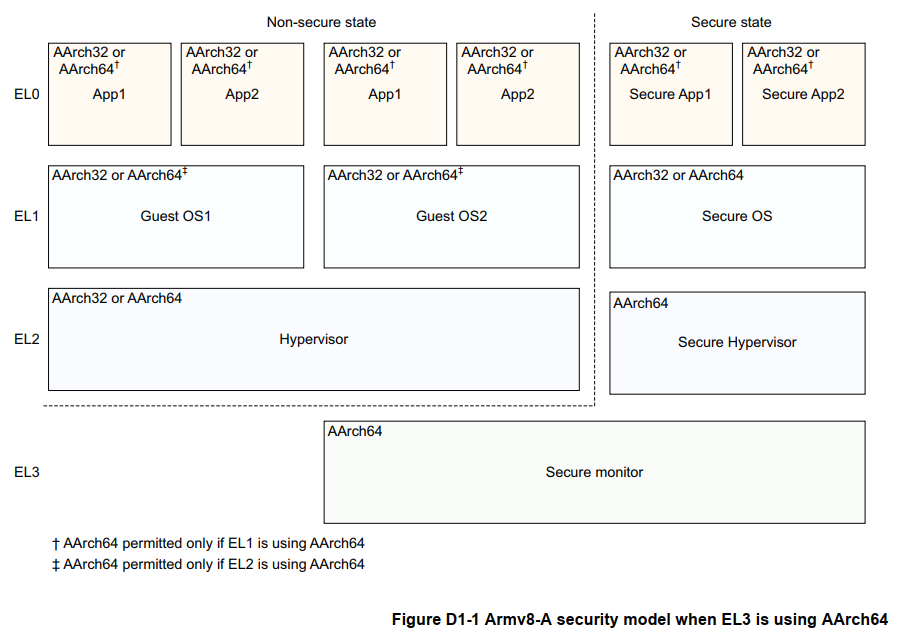

5.1 EL3使用AArch64时(注意两个图的差别和脚注)

5.2 EL3使用AArch32时

5.2.1 Armv8-A Security model when EL3 is using AArch32

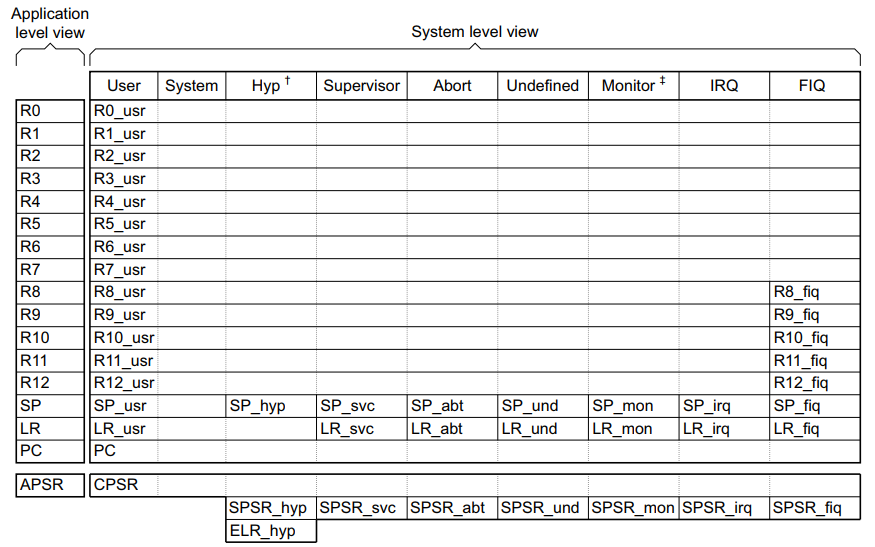

5.2.2 AArch32 PE modes

5.2.3 AArch32 通用寄存器, PC, 和特殊寄存器 一览表

参考:

(1) 《Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile - The AArch64 System Level Memory Model D4.4 Cache support》。

(2) ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(1)-EL/ET/ST(注意本文部分描述有误)